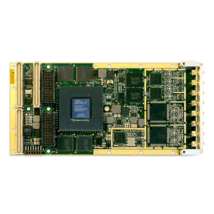

The X6-RX is a flexible receiver that integrates IF digitizing with signal processing on a PMC IO module. The module provides up to 24 configurable receiver channels with a powerful Xilinx Virtex 6 FPGA signal processing core, and high performance PCI Express/PCI host interface. With the X6-RX, IF recorders can log both the digitized raw data and channels real-time sustaining rates over 2 GB/s.

The X6-RX features four, 16-bit 160 MSPS A/Ds. IF frequencies of up to 300 MHz are supported. The sample clock is from either a low-jitter PLL or external input. Multiple cards can be synchronized for sampling and downconversion.

A Xilinx Virtex6 SX315T (LX240T at initial release) with 4 banks of 1GB DRAM provide a very high performance DSP core with over 2000 MACs (SX315T). The close integration of the analog IO, memory and host interface with the FPGA enables real-time signal processing at extremely high rates.

The X6 family power is less than 15W for typical operation. VITA 20 conduction cooling is used with a heat-spreader and sink are Ruggedization levels for wide-temperature operation and conformal coating are supported.

The FPGA logic can be fully customized using VHDL and MATLAB using the Frame Work Logic toolset. The MATLAB BSP supports real-time hardware-inthe-loop development using the graphical, block diagram Simulink environment with Xilinx System Generator. IP cores for DDC, demodulation, and FFT are available.

Software tools for host development include C++ libraries and drivers for Windows and Linux. Application examples demonstrating the module features and use are provided.